mm7-pwb

mm-7 のプリント基板

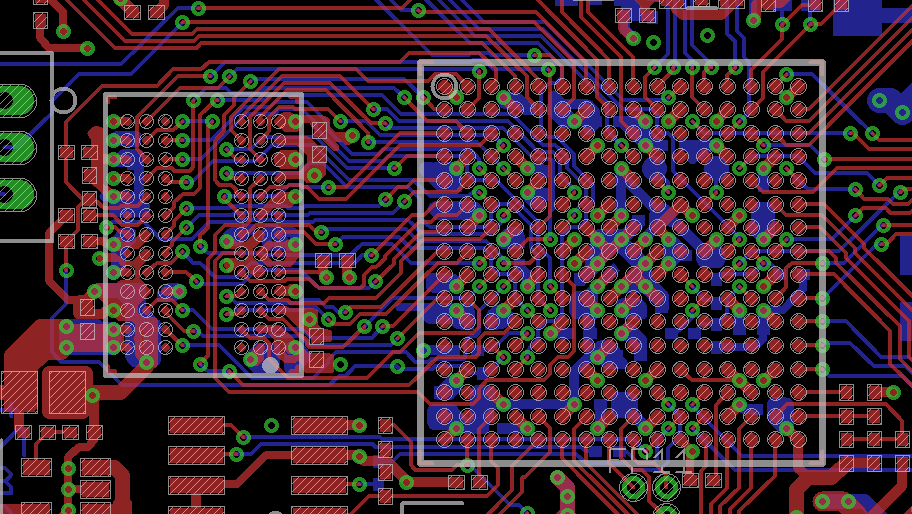

DDR3 の実装

mm-7のプリント基板は 4層板で、P板.com の標準デザインルールの範囲で設計しました。

今回は、1mmピッチ256ボールのFPGAに加え、0.8mmピッチ78ボールのDDR3を実装しました。

FPGAとDDR3の接続は、FPGA側のピン配置がメモリーコントローラで固定されているため自由に選べません。DDR3はデータバスx16のものまでありますが、4層基板でP板.com標準ルールで接続するのはかなり難しく、データバスx8を接続するのがやっとでした。

DDRのデータ転送速度は、FPGAのスピードバージョン-2 の上限付近の624Mbps としました。DDR3は1333Mbps品なので余裕はありそうですが、伝送路シミュレーションなどは出来ないので、どれくらいタイミングマージンがあるかは不明です。

配線は、CK/CK# DQS/DQS# の差動ペアを優先的に引き、次にデータバスDQを引き、高速のラインを極力短く引きました。

また、電源のパスコンは、1005サイズの1uFセラミックをできるだけ電源ピンの付近の部品面に配置しました。

Xilinx のツール(coregen)を使ってメモリコントローラをコンフィグレーションすると、メモリコントローラのRTLや、シミュレーション環境、合成環境の他に、example_design が生成されます。example_designは擬似ランダムパターンなどを発生してメモリに書き込み、読み出してコンペアし続ける、テスト回路です。

まずはこれを用いて論理シミュレーションで動作を確かめ、FPGAにロードしてメモリの動作確認、耐久テストを行いました。その結果、充分安定に動作することが確かめられました。データバスのターミネーションは省電力のためOFFにしています。

(Xilinx のツールiseの無償バージョン(Web-Pack)のシミュレータは、回路規模の制限を越えるとシミュレーション速度が実用にならないほど低下する使用制限がかかります。メモリコントローラを使った時点でこの制限を越えてしまうので、30日間の評価ライセンスを取得して制限を解除することでなんとか設計を進めました)