mm7-system

mm-7/ハードウエア

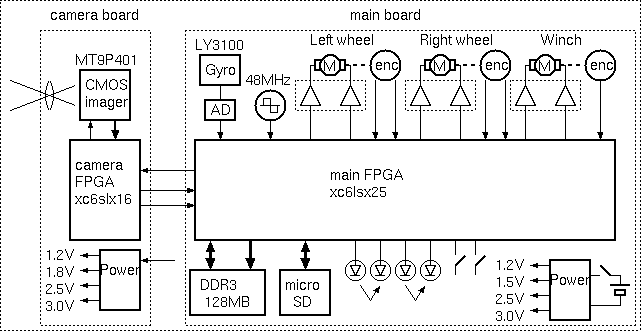

システム構成

mm-7 のシステム構成です。

カメラ基板とメイン基板それぞれXilinx社のFPGA Spartan-6 を中心にシステムを組んでいます。

それぞれのFPGAにオリジナル設計のCPUを搭載しています。

カメラ基板のFPGAは、CMOSセンサーの制御と画像データの色差画像への変換を行い、高速差動シリアル信号にしてメイン基板へ送ります。

メイン基板のFPGAは、カメラ基板からの画像データをDDR3メモリに書き込み、CPUからDDR3にアクセスして画像処理を行い、迷路を解析します。迷路解析後の走行制御には反射型光センサーを使いました。カメラは視野が狭く、自身の近辺が見えません。

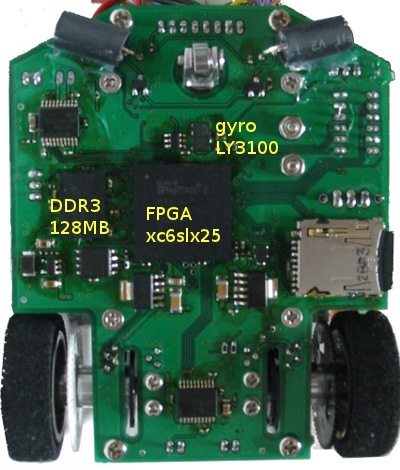

左:メイン基板です。

FPGA、DDR3 の2つのBGAをオーブントースターでリフロー実装しました。→mm-6の実装

下:カメラ基板です。

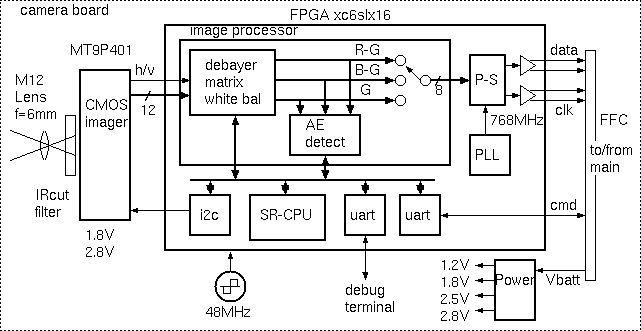

カメラ基板

カメラ基板のブロック図です。

CMOSセンサーMT9P401は 2592x1944 画素のカラーセンサーです。i2cバスで駆動モードや各種パラメータを設定します。画像データは12bitで最大96MHzのディジタルデータとして出力されます。

カメラ基板のFPGAにはSR-CPUを組み込み、CMOSセンサーのコントロールを行います。

センサーから出力されたRGB三色のデータからdebayer,matrix回路で8bitの色差信号を作ります。

CPUは 赤、青、の色差信号の平均値を測定し、色差の平均値が0に近づくように、センサーの赤信号ゲイン、青信号ゲインを制御します。(ホワイトバランス制御)

また、緑信号のレベルを測定し、適度な露出になるようにセンサーの電子シャッター速度を制御します。(AE、露光制御)

適正に調整された色差データをメイン基板に送るため、8ビットを1ビットシリアルの高速データにし、(96MHzx8=768Mbps)LVDS差動信号で伝送します。カメラを高く持ち上げるため、柔軟な FFC(フレキシブルフラットケーブル)でメインとつないでいますので、安定に高速データを伝送するには差動伝送が適当です。

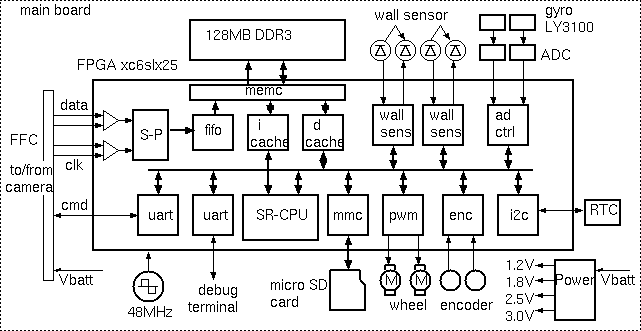

メイン基板

メイン基板のブロック図です。

カメラ基板からの高速シリアルデータをLVDSレシーバで受信し、8bitパラレルデータに変換してDDR3 DRAMに書き込みます。

Spartan-6のシリアルパラレル変換ユニットはクロックとデータの位相差を自動調整する機能を持っています。自宅のオシロスコープでは768Mbpsのデータ波形はまったく確認できませんが、無調整で安定に伝送できています。

DDR3 DRAM はXilinx のMIG(メモリインタフェースジェネレータ)で生成したメモリコントローラで接続しており、624Mbpsで接続しています。専用のメモリインターフェースマクロですので安定に接続出来ています。

メインのCPUからは命令及びデータキャッシュを介してメモリコントローラに接続しています。DRAMをCPUのアドレス空間に直接マッピングしてメモリ上の画像を処理しています。

また、プログラムはSDカードからロードして実行するようにしていますが、内蔵SRAMに収まりきれないプログラムはDRAM上にロードして実行します。